# Implementation of Different PWM Control Strategies for Cascaded MLI

M.Dharani Devi <sup>1</sup>, R.Nagarajan <sup>2</sup>

<sup>1</sup>Associate Professor, Department of Electrical and Electronics Engineering, M.A.M. School of Engineering, Trichy, India.

<sup>2</sup>Professor, Department of Electrical and Electronics Engineering, Gnanamani College of Technology, Namakkal, India.

Abstract -In this paper, investigates and analysis the performance of the novel pulse width modulation techniques which uses stepped carrier waveforms are proposed for five-level cascaded inverter. In each carrier waveform, different techniques such as phase disposition (PD), inverted phase disposition (IPD), phase opposition disposition (POD) and alternative phase opposition disposition (APOD) implemented. The fundamental output voltage and harmonics obtained in each method are compared with the output waveform obtained with the triangular carrier waveform. The different PWM methodologies adopting the constant switching frequency multicarrier with different modulation indexes are simulated for a 1kW, 3\phi cascaded multilevel inverter using MATLAB/SIMULINK and the effect of switching frequency on the fundamental output voltage and harmonics are also analyzed. The proposed switching technique enhances the fundamental component of the output voltage and reduces the total harmonic distortion.

Index Terms – Modulation Index (MI), Sinusoidal Pulse Width Modulation (SPWM), Total Harmonic Distortion (THD),

#### 1. INTRODUCTION

Multilevel inverter is an effective solution for increasing power and reducing harmonics of AC waveform [1]. The elementary concept of a multilevel converter to achieve higher power is to use a series of power semiconductor switches with several lower voltage DC sources to perform the power conversion by synthesizing a staircase voltage waveform. Capacitors, batteries, and renewable energy voltage sources can be used as the multiple DC voltage sources. The commutation of the power switches aggregate these multiple DC sources in order to achieve high voltage at the output; however, the rated voltage of the power semiconductor switches depends only upon the rating of the DC voltage sources to which they are connected [2].

In this paper, constant switching frequency multicarrier pulse width modulation method is used for the multilevel inverter [3]. The control objective is to compare the reference sine wave with multicarrier waves for three phase five level cascaded inverters. Multilevel voltage source inverter (MVSI) structure is very popular especially in high power DC to AC

power conversion applications. It offers several advantages that make it preferable over the conventional voltage source inverter (VSI). These include the capability to handle higher DC link voltage; the stress on each switching device can be reduced in proportional to the higher voltages [4], [5]. Consequently, in some applications, it is possible to avoid expensive and bulky step-up transformer. Another significant advantage of a multilevel output is better sinusoidal voltage waveform. As a result, a lower total harmonic distortion (THD) is obtained [6].

The concept of multilevel converter has been introduced since 1975. The term multilevel began with the three-level converter. Subsequently, several multilevel converter topologies have been developed, such as the Diode Clamped Multilevel Inverter (DCMLI) also known as Neutral Point Clamped (NPC) Inverter, Flying Capacitor Multilevel Inverter (FCMLI) and Cascaded Multilevel Inverter (CCMLI) [7], [8]. Among them, CCMLI topology is the most attractive, since it requires the least number of components and increases the number of levels in the inverter without requiring high ratings on individual devices and the power rating of the CCMLI is also increased [9]. [10]. It also results in simple circuit layout and is modular in structure. Furthermore, CCMLI type of topology is free of DC voltage balancing problem, which is a common issue facing in the DCMLI and FCMLI topologies.

Numerous industrial applications have begun to require higher power apparatus in recent years. Some medium voltage motor drives and utility applications require medium voltage and megawatt power level. For a medium voltage grid, it is troublesome to connect only one power semiconductor switch directly [11].

As a result, a multilevel power converter structure has been introduced as an alternative in high power and medium voltage situations. A multilevel converter not only achieves high power ratings, but also enables the use of renewable energy sources. Renewable energy sources such as photovoltaic, wind, and fuel cells can be easily interfaced to a multilevel converter system for high power application [12]

In motor applications, high dv/dt in power supply generates high stress on motor windings and requires additional motor insulation. Further; high dv/dt of semiconductor devices increases the electromagnetic interference (EMI), commonmode voltage and possibilities of failure on motor. By increasing the number of levels in the output waveform, the switching dv/dt stress is reduced in the multilevel inverter [13], [14]. Multilevel inverters are suitable for power electronics applications such as flexible AC transmission systems, renewable energy sources, uninterruptible power supplies, electrical drives and active power filters [15], [16].

#### 2. CASCADED MULTILEVEL INVERTER

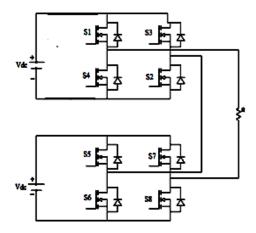

The single-phase structure of three phase five-level cascaded inverter is illustrated in Figure 1. Each separate DC source is connected to a single-phase full-bridge, or H-bridge, inverter. Each inverter can generate three different outputs voltage level,  $+V_{dc}$ , 0 and  $-V_{dc}$ , by connecting the DC source to the AC output by different switching combinations of the four semiconductor switches S1, S2, S3 and S4. To obtain  $+V_{dc}$ , switches S1 and S2 are tuned on ,whereas  $-V_{dc}$  can be obtained by tuning on switches S3 and S4, By turning on S1 and S3 or S2 and S4, the output voltage is 0, The AC outputs of each of the full-bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the inverter outputs [17], [18].

Figure 1, 1∮ Structure of Five-Level Cascaded Inverter

The CCMLI is producing five level output and they are  $2V_{\rm dc}$ ,  $V_{\rm dc}$ , 0,  $V_{\rm dc}$  and  $-2V_{\rm dc}$ . This topology is suitable for applications where separate DC voltage sources are available, such as photovoltaic (PV) generators, fuel cells and batteries. The phase output voltage is generated by the sum of two output voltage of the full bridge inverter modules. The circuit in Figure 1 utilizes two independent DC sources and consequently will create an output phase voltage with fivelevel. In general, if N is the number of independent DC sources per phase, then the following relations apply [19]:

$$m = 2N + 1 \tag{1}$$

$$q = 2(m-1) \tag{2}$$

Where m is the number of levels and q is the number of switching devices in each phase

The most well known SPWM which can be applied to a CCMLI is the Phase-Shifted SPWM. This modulation technique is the same as that of the conventional SPWM technique which is applied to a conventional single phase full-bridge inverter, the only difference being that it utilizes more than one carrier. The number of carriers to be used per phase is equal to twice the number of DC voltage sources per phase (2N) [20]. The simulation results are obtained for the output phase voltage and line voltage of the three phase five-level CCMLI with 1KW,  $3\phi$  resistive loads for various PWM techniques.

# 3. MODULATION TECHNIQUES

The Pulse Width Modulation (PWM) control strategies development tries to reduce the total harmonic distortion (THD) of the output voltage. Any deviation in the output voltage of the sinusoidal wave shape will result in harmonic currents in the load and this harmonic current produces the electromagnetic interference (EMI), harmonic losses and torque pulsation in the case of motor drives. Increasing the switching frequency of the PWM pattern reduces the lower frequency harmonics by moving the switching frequency carrier harmonic and associated sideband harmonics away from the fundamental frequency component [21], [22]. This increased switching frequency reduces harmonics, which results in a lower THD with high quality output voltage waveforms of desired fundamental RMS value and frequency which are as close as possible to sinusoidal wave shape. The carrier frequency defines the switching frequency of the converter and the high order harmonic components of the output voltage spectrum and the sidebands occur around the carrier frequency and its multiples. The higher switching frequency can be employed for low and medium power inverters, whereas, for high power and medium voltage applications the switching frequency should be low. Harmonic reduction can then be strictly related to the performance of an inverter with any switching strategy [23], [24].

The three phase multilevel inverter requires three modulating signals or reference signals which are three sine-waves with 120 degree phase shift and equal in magnitudes. In this paper, new carrier based PWM techniques are developed which are as Stepped Multicarrier Sinusoidal PWM (SMC SPWM).

Each carrier is to be compared with the corresponding modulating sine wave [25], [26]. The reference or modulation

waveform has peak amplitude  $A_r$  and frequency  $f_r$  and it is centered in the middle of the carrier set. The general principle of a carrier based PWM technique is the comparison of a sinusoidal waveform with a carrier waveform, this typically being a triangular carrier waveform. The reference is continuously compared with the carrier signal. If the reference is greater than the carrier signal, then the active device corresponding to that carrier is switched on, and if the reference is less than the carrier signal, then the active device corresponding to that carrier is switched off [27], [28]. In multilevel inverters, the amplitude modulation index,  $M_a$  and the frequency ratio,  $M_f$  are defined as,

$$M_a = \frac{A_r}{(m-1)A_c} \tag{3}$$

$$M_{f} = \frac{f_{c}}{f_{r}} \tag{4}$$

Where  $A_r$  and  $A_c$  are amplitude of reference and carrier signal respectively.  $f_r$  and  $f_c$  are frequency of reference and carrier signal respectively.

In this paper, modulation indexes used are 0.6, 0.7, 0.8, 0.9 and 1 for five-level CCMLI. For multilevel applications, carrier based PWM techniques with multiple carriers are used. The Multicarrier Modulation (MCM) techniques, can be divided in to the following categories [29], [30] such as,

- 1. Phase disposition (PD) where all the carriers are in phase.

- 2. Inverted phase disposition (IPD) where all the carriers are in phase and is inverted.

- 3. Phase opposition disposition (POD) where the carriers above the zero reference are in phase but shifted by 180 degrees from those carriers below the zero reference.

- 4. Alternative phase opposition disposition (APOD) where each carrier band is shifted by 180 degrees from the adjacent carrier bands [2].

The above modulation strategies are implemented for different carriers such as stepped wave. The phase voltage and line voltage waveform, harmonic spectrums of the line voltage are shown for different modulation techniques by doing simulation using MATLAB/SIMULINK for a five level CCMLI and the results obtained are compared.

## 3.1. Triangular Multicarrier Sinusoidal PWM (TMC SPWM)

The performance of the multilevel inverter is based on the multicarrier modulation technique used. Two-level to multilevel inverters are made using several triangular carrier signals and one reference signal per phase. Carrara [5] developed multilevel sub harmonic PWM (SH-PWM), which is as follows, for m-level inverter, m-1 carriers [31] with the same frequency  $f_c$  and same amplitude  $A_c$  are disposed such

that the bands they occupy are contiguous. They are defined as

$$C_{i} = A_{c} \left( (-1)^{f(i)} y_{c}(\omega_{c}, \varphi) + t - \frac{m}{2} \right), \qquad (5)$$

$$i = 1, \dots, (m-1)$$

Where  $y_c$  is a normalized symmetrical triangular carrier defined as,

$$y_{c}(\omega_{c}, \varphi) = (-1)^{[\alpha]} ((\alpha \mod 2) - 1) + \frac{1}{2}$$

(6)

$$\alpha = \frac{\omega_{\rm C}t + \varphi}{\pi}, \omega_{\rm C} = 2\pi f_{\rm C} \tag{7}$$

$\phi$  represents the phase angle of  $y_c$ .  $y_c$  is a periodic function with the period  $T_C = \frac{2\pi}{\omega_C}$ . It is shown that using symmetrical

triangular carrier generates less harmonic distortion at the inverters output [32], [33].

In TMC SPWM, so far only the PD, POD and APOD techniques are discussed earlier in the literature. In this paper, IPD scheme is also applied to TMC SPWM and it is found that this scheme gives the lowest THD among the TMC SPWM schemes.

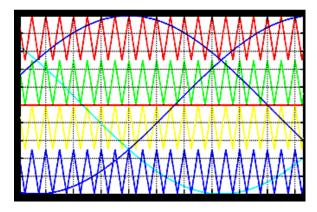

The multicarrier modulation techniques (PD, IPD, POD and APOD) are implemented using triangular multicarrier signals for five-level CCMLI with different modulation indexes and are shown in Figure 2.

Figure 2 IPD TMC SPWM with  $M_a=1$  for five-level CCMLI

# 3.2. Stepped Multicarrier Sinusoidal PWM (SMC SPWM)

The stepped wave is also known as approximated or modified sine wave, refers to a sine wave that instead of looking like a smooth curve where the wave gradually ramps up and down over the course of the cycle, there are a series of "steps" or jumps in wave from one plateau to another [34]. The simulink block provides a step between two definable levels at a specified time. Each cycle constitutes eight steps. Every step

is equal in magnitude and in time [35]-[37]. At the beginning and ending of the cycle, the signal has magnitude zero and retains for half the value of the one step time period. The angle of each step is  $\varphi$  which is given by (8).

$$\varphi = \frac{360^{\circ}}{n_{S}} \tag{8}$$

Where  $n_s$  is the number of steps in one cycle, since  $n_{s=}8$  the angle for each step is  $45^{\circ}$ .

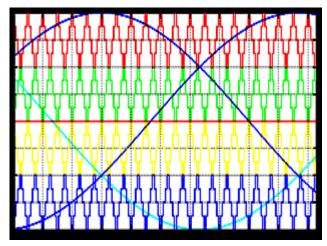

The multicarrier modulation techniques (PD, IPD, POD and APOD) are implemented using Stepped multicarrier signals for five-level CCMLI with different modulation indexes and are shown in Figure 3 respectively.

Figure 3 APOD SMC SPWM with Ma=1 for five-level CCMLI

#### 4. SIMULATION RESULTS

The five level cascaded multilevel inverter model with different modulation indexes was implemented in MATLAB/SIMULINK software to demonstrate the feasibility of PWM techniques. Phase disposition, inverted phase disposition, phase opposition disposition and alternative phase opposition disposition techniques are used for the various multicarrier SPWM techniques such as;

- Triangular Multicarrier Sinusoidal PWM

- 2. Stepped Multicarrier Sinusoidal PWM

The line voltage waveform with its harmonic spectrum at fundamental frequency of 50Hz and switching frequency of 2 KHz and 10 KHz are obtained for the proposed CCMLI. For comparison, the total harmonic distortion (THD) was chosen to be evaluated for all the modulation techniques. In order to get THD level of the waveform, a Fast Fourier Transform (FFT) is applied to obtain the spectrum of the output voltage. The THD is calculated using the following equation in this work.

$$THD = \frac{\sqrt{\sum_{n=2}^{80} v_n^2}}{v_1}$$

(9)

Where n is the harmonic order,  $v_n$  is the RMS value of the n<sup>th</sup> harmonic component and  $v_1$  is the RMS value of the fundamental component. Here the %THD is calculated up to a harmonic order which is twice the switching frequency. For 2 KHz switching frequency up to  $80^{th}$  order harmonics is taken in to account for calculating THD and for 10 KHz switching frequency up to  $400^{th}$  order harmonics is taken in to account for calculating THD.

# 4.1. Triangular Multi Carrier SPWM (TMC SPWM)

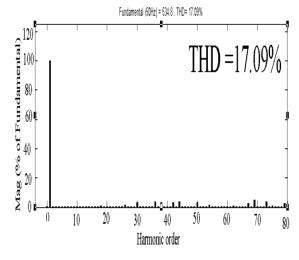

Figure 4(a) and 4(b) show the line voltage waveforms and the percentage THD of the line voltage for five level using the inverted phase disposition technique for triangular multi carrier sinusoidal PWM with Ma=1.

Figure 4(a) Line Voltage for IPD SPWM with Ma=1

Figure 4(b): Line Voltage %THD for IPD SPWM with Ma=1

Table1: Line voltage %THD for CCMLI with TMC SPWM

| Switching frequency | Modulation | Modulation Indexes |             |             |             |             |  |  |

|---------------------|------------|--------------------|-------------|-------------|-------------|-------------|--|--|

|                     | Technique  | $M_a=1$            | $M_a = 0.9$ | $M_a = 0.8$ | $M_a = 0.7$ | $M_a = 0.6$ |  |  |

| 2KHz                | PD         | 17.11              | 17.55       | 21.73       | 24.14       | 25.62       |  |  |

|                     | IPD        | 17.09              | 17.55       | 21.73       | 24.14       | 25.62       |  |  |

|                     | POD        | 21.89              | 29.94       | 35.48       | 38.65       | 38.42       |  |  |

|                     | APOD       | 25.66              | 28.75       | 29.75       | 28.04       | 25.93       |  |  |

| 10KHz               | PD         | 17.58              | 17.77       | 21.81       | 24.21       | 28.03       |  |  |

|                     | IPD        | 17.56              | 17.77       | 21.81       | 24.21       | 28.03       |  |  |

|                     | POD        | 23.91              | 31.42       | 36.45       | 38.63       | 37.68       |  |  |

|                     | APOD       | 27.07              | 29.57       | 30.46       | 28.85       | 29.33       |  |  |

|                     |            |                    |             |             |             |             |  |  |

Table 1 shows the percentage line voltage THD for the five-level CCMLI with triangular multicarrier signal with different multicarrier PWM techniques with a switching frequency of 2 KHz and 10 KHz respectively for different modulation indexes.

From the above table, it is observed that, when the switching frequency of the CCMLI is increased, the percentage line voltage THD is increased for the PD and IPD schemes with all modulation indexes. In the POD scheme, if the switching frequency is increased, the percentage line voltage THD is reduced with modulation index of 0.7 and 0.6. In the APOD scheme, when the switching frequency is increased, the percentage line voltage THD is increased with all modulation indexes, in five-level CCMLI.

From the simulation result in the triangular multicarrier SPWM technique PD and IPD PWM schemes, from 3<sup>rd</sup> order harmonics to 25th order harmonics are less than 1%. Few of the odd and even order harmonics from 26th harmonics to 79th harmonics are present. The dominant 69th harmonic factor is about 5% for the PD and IPD schemes. In the POD scheme, from 3<sup>rd</sup> odd order harmonics to 27<sup>th</sup> odd order harmonics are less than 1% and all even order harmonics are zero. Few of the odd order harmonics from 29th harmonics to 79th harmonics are 1% to 3%. The dominant 39th and 41st harmonic factor are 10.29% and 10.46% respectively for the POD scheme. In the APOD scheme, from 3rd odd order harmonics to 31st odd order harmonics are less than 1% and all even order harmonics are 0.03%. Few of the odd order harmonics from 33<sup>rd</sup> harmonics to 79<sup>th</sup> harmonics are present. The dominant 35th and 45th harmonic factor are 11.94% and 11.87% respectively for the APOD scheme.

## 4.2 Stepped Multi Carrier SPWM (SMC SPWM)

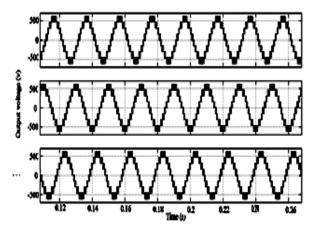

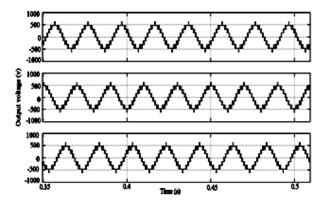

Figure 5(a) and 5(b) show the line voltage waveforms and the percentage THD of the line voltage for five level using the phase disposition technique for stepped multi carrier

sinusoidal PWM with Ma=0.9.

Figure 5(a) Line Voltage for PD SPWM with Ma=0.9

Figure 5(b) Line Voltage %THD for PD SPWM with Ma=0.9

Table 2 shows the percentage line voltage THD for the five-level CCMLI with stepped multicarrier signal with different multicarrier PWM techniques with a switching frequency of 2 KHz and 10 KHz respectively for different modulation indexes.

Table2: Line voltage %THD for CCMLI with SMC SPWM

| Switching | Modulation | Modulation Indexes |             |             |             |             |  |  |  |

|-----------|------------|--------------------|-------------|-------------|-------------|-------------|--|--|--|

| frequency | Technique  |                    |             |             |             |             |  |  |  |

|           |            | $M_a=1$            | $M_a = 0.9$ | $M_a = 0.8$ | $M_a = 0.7$ | $M_a = 0.6$ |  |  |  |

|           | PD         | 17.65              | 15.79       | 21.89       | 23.42       | 27.47       |  |  |  |

| 2KHz      | IPD        | 17.63              | 15.79       | 21.89       | 23.42       | 27.47       |  |  |  |

|           | POD        | 25.20              | 29.56       | 36.07       | 39.72       | 40.17       |  |  |  |

|           | APOD       | 27.83              | 29.04       | 30.12       | 29.21       | 29.25       |  |  |  |

|           | PD         | 17.41              | 15.82       | 22.45       | 23.71       | 26.45       |  |  |  |

| 10KHz     | IPD        | 17.39              | 15.82       | 22.45       | 23.71       | 26.45       |  |  |  |

|           | POD        | 23.11              | 26.97       | 33.90       | 37.39       | 36.61       |  |  |  |

|           | APOD       | 25.45              | 26.25       | 29.18       | 28.22       | 27.94       |  |  |  |

|           |            |                    |             |             |             |             |  |  |  |

From the above table, it is observed that, when the switching frequency of the CCMLI is increased, the percentage line voltage THD is reduced for the PD and IPD schemes with modulation index of 1 and 0.6. In the POD and APOD schemes, if the switching frequency is increased, the percentage line voltage THD is reduced with all modulation indexes, in five-level CCMLI.

From the simulation result in the stepped multicarrier SPWM technique PD and IPD PWM schemes, from 3rd order harmonics to 27th order harmonics are less than 1%. Few of the odd and even order harmonics from 28th harmonics to 79th harmonics are 1% to 3%. The dominant 69<sup>th</sup> harmonic factor is about 4% for the PD and IPD schemes. In the POD scheme, from 3<sup>rd</sup> odd order harmonics to 27<sup>th</sup> odd order harmonics are less than 1% and all even order harmonics are 0.03%. Few of the odd order harmonics from 29th harmonics to 79th harmonics are 1% to 3%. The dominant 39th and 41st harmonic factor are 12.22% and 12.87% respectively for the POD scheme. In the APOD scheme, from 3rd odd order harmonics to 31st odd order harmonics are less than 1% and all even order harmonics are 0.03%. Few of the odd order harmonics from 33<sup>rd</sup> harmonics to 79<sup>th</sup> harmonics are present. The dominant 35th and 45th harmonic factor are 10.30% and 9.79% respectively for the APOD scheme.

## 5. CONCLUSION

In this paper, the performance of different multicarrier PWM techniques which uses triangular multicarrier waveform, stepped multicarrier waveform in multilevel inverters are found out. In all the above PWM techniques, different modulation strategies such as phase disposition (PD), inverted phase disposition (IPD), phase opposition disposition (POD) and alternative phase opposition disposition (APOD) are implemented. The results are verified by doing simulation for a 1kW, three-phase five-level cascaded inverter in MATLAB/SIMULINK. The output quantities fundamental phase and line voltage, percentage THD of the line voltage and percentage dominant harmonic factor are measured in the all the above PWM schemes and the results are compared.

#### **REFERENCES**

- Mariusz Malinowski, K. Gopakumar, Jose Rodriguezand Marcelo A. Pérez, "A Survey on Cascaded Multilevel Inverters" IEEE Transactions on Industrial Electronics, vol. 57, n. 7, July 2010, pp 2197 – 2206.

- [2] R.Nagarajan and M,Saravanan, "Performance Analysis of Multicarrier PWM Strategies for Cascaded Multilevel Inverter," European Journal of Scientific Research (EJSR), Vol.92 No.4, pp. 608-625, Dec. 2012.

- [3] Jang-Hwan Kim, A carrier-Based PWM Method for Three-Phase Four-Leg Voltage Source Converters", IEEE transactions on power electronics, vol. 19, n.1, January 2004.

- [4] R.Nagarajan and M,Saravanan, "A Carrier Based Pulse Width Modulation Control Strategies for Cascaded Multilevel Inverter," International Review on Modeling and Simulations (IRMOS), Vol 6.No1, pp-8-19, Feb. 2013.

- [5] G.Carrara, S.Gardella, M.Marchesoni, R.Salutari, G.Sciutto, "A New Multilevel PWM Method: A Theoretical Analysis," IEEE Trans. Power Electronics, vol. 7, n.3, July 1992, pp 497-505.

- [6] R.Nagarajan and M, Saravanan, "Comparison of PWM Control Techniques for Cascaded Multilevel Inverter" International Review of Automatic control (IRACO), Vol.5, No.6, pp. 815-828. Nov. 2012.

- [7] G. Vidhya Krishnan, R.Nagarajan, T. Durka, M.Kalaiselvi, M.Pushpa and S. Shanmuga priya, "Vehicle Communication System Using Li-Fi Technology," International Journal of Engineering And Computer Science (IJECS), Volume 6, Issue 3, pp. 20651-20657, March 2017.

- [8] S.M.Ayob, Z.Salam, "Trapezoidal PWM Scheme for Cascaded Multilevel Inverter" First International Power and Energy Conference, November 2006, pp 368-372.

- [9] R.Prabhu, R.Nagarajan, N.Karthick and S.Suresh, "Implementation of Direct Sequence Spread Spectrum Communication System Using FPGA," International Journal of Advanced Engineering, Management and Science (IJAEMS), Vol-3.Issue-5, pp. 488-496, May. 2017

- [10] Rodriguez, Jih-sheng lai, and F.Zheng peng, "Multilevel Inverters; A Survey of Topologies, Controls, and Applications," IEEE Trans.Ind.Electron, vol.49, n. 4, pp724-738, Aug.2002.

- [11] A.Mahendran, K.Muthulakshmi and R.Nagarajan, "Triangular Multicarrier SPWM Technique for Nine Level Cascaded Inverter," International Journal of Scientific & Engineering Research, Vol.4, No.5, pp. 269-275, May-2013.

- [12] C.Mallika devi and R.Nagarajan, "High-Power Transformer-Less Wind Energy Conversion System with three phase Cascaded Multilevel Inverter," International Journal of Scientific & Engineering Research. Vol. 4, Issue- 5, pp. 67-70, May-2013.

- [13] J.Chandramohan, R.Nagarajan, K.Satheeshkumar, N.Ajithkumar, P.A.Gopinath and S.Ranjithkumar, "Intelligent Smart Home Automation and Security System Using Arduino and Wi-fi," International Journal of Engineering And Computer Science (IJECS), Volume 6, Issue 3, pp. 20694-20698, March, 2017.

- [14] Samir koaro, PabloLezana, Mauricio Anguio and Jose Rodriguez, "Multicarrier PWM DC-Link ripple forward compensation for multilevel inverters," IEEE Trans. Power.Electron., vol.123, n.1, pp.52-56, Jan 2008.

- [15] K. Anandhi and Dr. R. Nagarajan, "Mutex-Heart: Fail Safe Dual Chamber Cardiac Pacemaker Device with Rate Responsive Control and Cryptographic Security," IJSRD- International Journal for Scientific Research & Development. Vol. 3, Issue- 2, pp. 489-493, 2015.

- [16] Fang Z. Peng, John W.Mckeever, and Donald J.Adams, "A Power line conditioner using Cascade Multilevel Inverters for Distribution systems" IEEE Transactions on Industrial Applications, vol. 34, n.6, pp 1293-1298, Nov/Dec 1998.

- [17] J.Chandramohan, R.Nagarajan, M.Ashok kumar, T.Dineshkumar, G.Kannan and R.Prakash, "Attendance Monitoring System of Students Based on Biometric and GPS Tracking System," International Journal of Advanced Engineering, Management and Science (IJAEMS), Vol-3.Issue-3, pp. 241-246, Mar. 2017.

- [18] B.P.Mcgrath, D.G.Holmes, "Multicarrier PWM strategies for multilevel inverters," IEEE Trans. Ind.Electron, vol 49, n.4, pp 858-867, Aug.2002.

- [19] R Rameshkumar and R Nagarajan, "Sine Multicarrier SPWM Technique for Seven Level Cascaded Inverter," CiiT-Programmable Device Circuits and Systems. Vol. 5, Issue- 6, 2013.

- [20] Dr.R.Nagarajan, S.Sathishkumar, K.Balasubramani, C.Boobalan, S.Naveen and N.Sridhar. "Chopper Fed Speed Control of DC Motor Using PI Controller," IOSR- Journal of Electrical and Electronics Engineering (IOSR-JEEE), Volume 11, Issue 3, Ver. I, pp. 65-69, May – Jun. 2016.

- [21] R.Nagarajan and M,Saravanan "Staircase Multicarrier SPWM Technique for Nine Level Cascaded Inverter," 2013 International Conference on Power, Energy and Control (ICPEC), IEEE Press, pp-668-675. 2013.

- [22] Lion M.Tolbert and Thomas.G.Habetler, "Novel Multi Level Inverter Carrier Based PWM methods", IEEE IAS, 1998, pp 1424-1431.

- [23] N.Karthick, R.Nagarajan, S.Suresh and R.Prabhu, "Implementation of Railway Track Crack Detection and Protection," International Journal Of Engineering And Computer Science (IJECS), Volume 6, Issue 5, May 2017, pp. 21476-21481, DOI: 10.18535/ijecs/v6i5.47

- [24] M.Padmavathi and R.Nagarajan, "Smart Intelligent ATM Using LABVIEW," International Journal of Emerging Technologies in Engineering Research (IJETER), Volume 5, Issue 5, pp. 41- 45, May-2017.

- [25] R.Nagarajan and M, Saravanan. "Performance Analysis of a Novel Reduced Switch Cascaded Multilevel Inverter," Journal of Power Electronics, Vol.14, No.1, pp. 48-60, Jan. 2014.

- [26] D.G.Holmes and T.A.Lipo, Pulse Width Modulation For Power Converters (Wiley Inter-science, 2003).J. Proakis, Digital Communications. New York: McGraw-Hill, 1995.

- [27] R.Nagarajan, S.Sathishkumar, S.Deepika, G.Keerthana, J.K.Kiruthika and R.Nandhini, "Implementation of Chopper Fed Speed Control of Separately Excited DC Motor Using PI Controller", International Journal of Engineering And Computer Science (IJECS), Volume 6, Issue 3, pp. 20629-20633, March, 2017.

- [28] D.G.Holmes and B.P.Mcgrath, "Opportunities for harmonic cancellation with carrier based PWM for two level and multilevel cascaded inverters", in conf.prec IEEE/IAS Annual meeting, 1999.

- [29] R.Nagarajan, R.Yuvaraj, V.Hemalatha, S.Logapriya, A.Mekala and S.Priyanga, "Implementation of PV - Based Boost Converter Using PI Controller with PSO Algorithm," International Journal of Engineering And Computer Science (IJECS), Volume 6, Issue 3, pp. 20479-20484, March, 2017.

- [30] Ms. C. Hemalatha, Mr. R. Nagarajan, P. Suresh, G. Ganesh Shankar and A. Vijay, "Brushless DC Motor Controlled by using Internet of Things," IJSTE - International Journal of Science Technology & Engineering, Volume -3.Issue-09, pp. 373-377, March-2017.

- [31] R.Nagarajan, J.Chandramohan, S.Sathishkumar, S.Anantharaj, G.Jayakumar, M.Visnukumar and R.Viswanathan, "Implementation of PI Controller for Boost Converter in PV System," International Journal of Advanced Research in Management, Architecture, Technology and Engineering (IJARMATE). Vol.11, Issue.XII, pp. 6-10, December. 2016.

- [32] M.Elangovan, R.Yuvara, S.Sathishkumar and R.Nagarajan, "Modelling and Simulation of High Gain Hybrid Boost Converter," International Journal of Emerging Technologies in Engineering Research (IJETER), Volume 5, Issue 6, pp. 9- 14, June-2017

- [33] S.Suresh, R.Nagarajan, L.Sakthivel, V.Logesh, C.Mohandass and G.Tamilselvan, "Transmission Line Fault Monitoring and Identification System by Using Internet of Things," International Journal of Advanced Engineering Research and Science (IJAERS), Vol - 4.Issue - 4, pp. 9-14, Apr- 2017.

- [34] R.Nagarajan, J.Chandramohan, R.Yuvaraj, S.Sathishkumar and S.Chandran, "Performance Analysis of Synchronous SEPIC Converter for a Stand-Alone PV System," International Journal of Emerging Technologies in Engineering Research (IJETER), Vol. 5, Issue - 5, pp. 12-16, May-2017

- [35] M. Sridhar, S.Sathishkumar, R.Nagarajan and R.Yuvaraj, "An Integrated High Gain Boost Resonant Converter for PV System," International Journal of Emerging Technologies in Engineering Research (IJETER), Volume 5, Issue 6, pp. 54- 59, June-2017.

[36] J.Hamman and F.S.Van Der merwe, "Voltage harmonics generated by

- [36] J.Hamman and F.S.Van Der merwe, "Voltage harmonics generated by voltage fed inverters using PWM natural sampling" IEEE Trans. Power Electron, vol PE-3,n.3, pp.297-302, Jul.1988.

- [37] S.Suresh, R.Nagarajan, R.Prabhu and N.Karthick, "Energy Efficient E0 Algorithm for Wireless Transceivers," International Journal of Engineering and Computer Science (IJECS), Volume 6, Issue 7, July 2017, pp. 21982-21985, DOI: 10.18535/ijecs/v6i7.15.

Authors

M. Dharani Devi received her B.E. in Electronics and Instrumentation Engineering from Madurai Kamaraj University, Madurai, India, in 2003. She received her M.E. in Process control and Instrumentation Engineering from Annamalai University, Chidambaram, India, in 2005. She has worked in the various institution as an Associate Professor. She is currently working as an Associate Professor of Electrical and Electronics Engineering at M.A.M.School of Engineering, Trichy, Tamilnadu,

India. Her research interest includes Process Control, Power Electronics and Renewable Energy Sources.

R. Nagarajan received his B.E. in Electrical and Electronics Engineering from Madurai Kamarajar University, Madurai, India, in 1997. He received his M.E. in Power Electronics and Drives from Anna University, Chennai, India, in 2008. He received his Ph.D in Electrical Engineering from Anna University, Chennai, India, in 2014. He has worked in the industry as an Electrical Engineer. He is currently working as Professor of Electrical and Electronics Engineering at Gnanamani College of

Technology, Namakkal, Tamilnadu, India. His current research interest includes Power Electronics, Power System, Soft Computing Techniques and Renewable Energy Sources.